# Rechnerstrukturen

2. Grundlagen

#### Inhalt

- ▼ Elektronische Schalter

- ▼ Elementare Gatterfunktionen

- ▼ Schaltnetze

- ▼ Schaltwerke

#### Motivation

- Unterscheidung von zwei Zuständen

- Strom / kein Strom

- Spannung / keine Spannung

- Positiv / Negativ geladen

- Reflektierend / nicht reflektierend

- ..

- Technische Umsetzung

- Mechanisch

- Elektromechanisch

- Elektronisch

- Licht

- ▼ Abbildung auf

- binäre Zahlen

- Wahrheitswerte

- Zeichen

2.3

## Elektronische Schalter

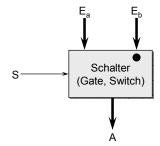

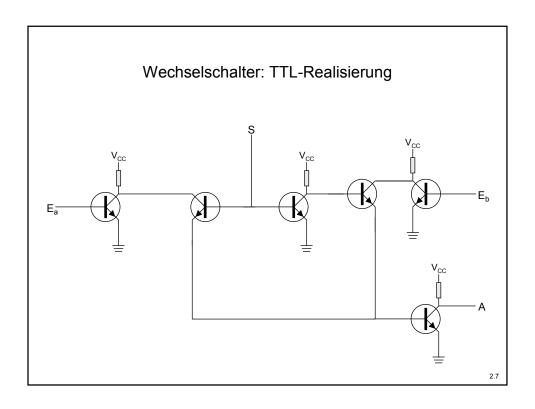

▼ Elementar Wechselschalter

$$A := E_a$$

else

$$A := E_b$$

- Vereinfachungen

- Ein Eingang konstant 0 oder 1

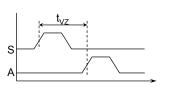

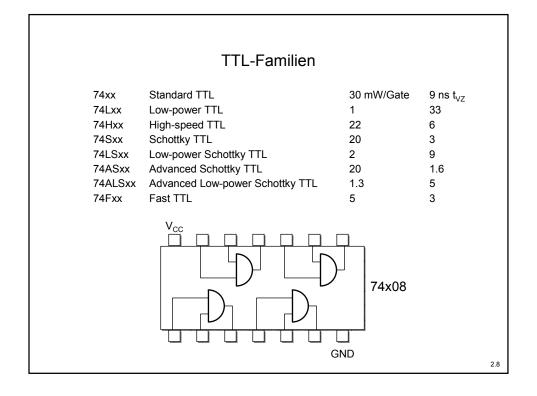

- ▼ Verzögerungszeit t<sub>∨7</sub>

- wird durch die eingesetzte Technologie bestimmt

- wenige Nanosekunden typisch

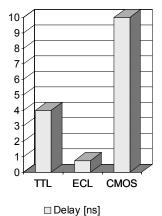

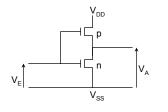

## Realisierungsvarianten

- ▼ Transistor-Transistor-Logik (TTL)

- ▼ Emitter-Coupled-Logik (ECL)

- Metal Oxid Semiconductor (MOS)

- Unterschiede

- Verzögerungszeit

- Versorgungsspannung

- 5 V (TTL)

- 2.8 3.3 V (MOS)

- Integrationsdichte

- 0.13μm 0.18μm (MOS)

- 0.08μm demnächst (MOS) (vgl. Haar = 100μm)

- Materialien

- Silicium, Aluminium

- in Zukunft ev. GaAs, Kupfer

2.5

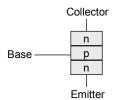

# Bipolare Transistoren

- ▼ npn- und pnp-Transistor

- Dotierung von Silicium

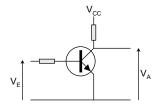

- ▼ Schaltverhalten

- $V_{E} = 0 V, V_{A} = 3 V$

- $V_E = 3 V, V_A = 0.2 V$

- ▼ Hohe Ströme

- p-Kanal muß mit Elektronen gefüllt werden

- Wärmeentwicklung

- Dicke der Leiterbahnen

- Geringe Kapazitäten

- ▼ Hohe Schaltgeschwindigkeit

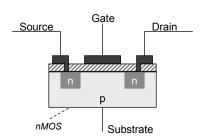

### Feldeffekttransistoren

- **FETs**

- NMOS (n-Kanal)

- PMOS (p-Kanal)

- CMOS (complementary MOS)

- NMOS und PMOS paarweise

- Schaltverhalten

- $\begin{array}{ll} & \mathsf{V_E} = \mathsf{0V}, \, \mathsf{VA} = \mathsf{V_{DD}} \\ & \mathsf{V_E} = \mathsf{V_{DD}} \,, \, \mathsf{VA} = \mathsf{0V} \end{array}$

- ▼ Längere Verzögerungszeit

- Kapazitives Element

- ▼ Geringe Spannungswerte

- Extrem geringe Ströme

2.9

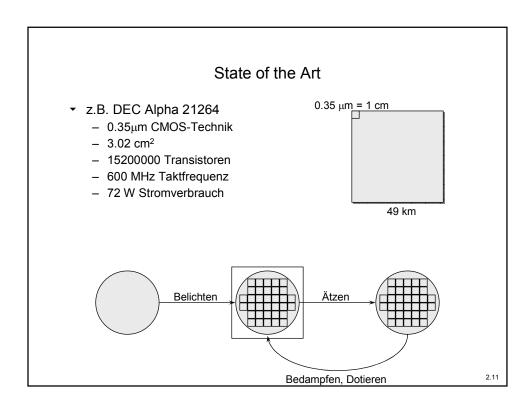

Wechselschalter: CMOS-Realisierung

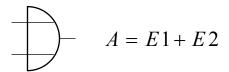

▼ UND

| E1 | E2 | A |

|----|----|---|

| 0  | 0  | 0 |

| 0  | 1  | 0 |

| 1  | 0  | 0 |

| 1  | 1  | 1 |

▼ ODER

| E1 | E2 | A |

|----|----|---|

| 0  | 0  | 0 |

| 0  | 1  | 1 |

| 1  | 0  | 1 |

| 1  | 1  | 1 |

▼ NICHT

2 1

NAND, NOR, XOR

- NIANID

| • | NAND |    |    |   |

|---|------|----|----|---|

|   |      | E1 | E2 | Α |

|   |      | 0  | 0  | 1 |

|   |      | 0  | 1  | 1 |

|   |      | 1  | 0  | 1 |

|   |      | 1  | 1  | 0 |

▼ NOR

| R |    |    |        |

|---|----|----|--------|

|   | E1 | E2 | Α      |

|   | 0  | 0  | 1      |

|   | 0  | 1  | 0      |

|   | 1  | 0  | 0<br>0 |

|   | 1  | 1  | 0      |

▼ XOF

| XUR   |    |    |   |

|-------|----|----|---|

| 7.01. | E1 | E2 | Α |

|       | 0  | 0  | 0 |

|       | 0  | 1  | 1 |

|       | 1  | 0  | 1 |

|       | 1  | 1  | 0 |

|       |    |    |   |

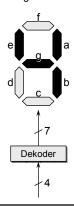

# Äquivalenz

- ▼ Ist XOR ein Grundgatter?

- Wieviele Grundgatter braucht man minimal, um beliebige boolesche Ausdrücke zu beschreiben?

2.15

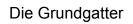

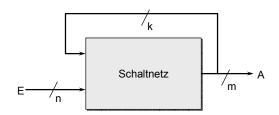

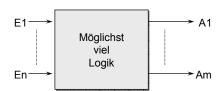

#### Schaltnetze

- ▼ Schaltung aus logischen Grundgattern mit

- n Eingängen

- m Ausgängen

- Rückkopplungsfrei

- ▼ 2n Eingangskombinationen

- m boolesche Ausdrücke über E1 ... En

- Wahrheitstabelle

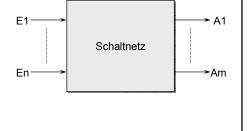

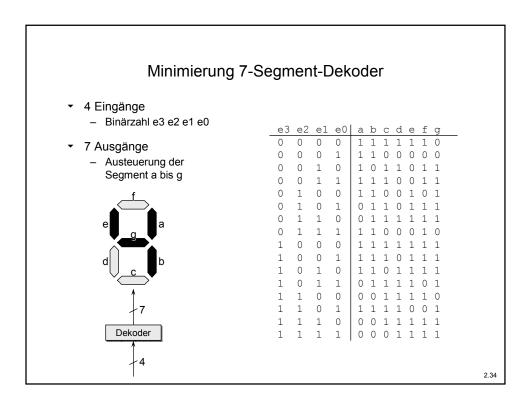

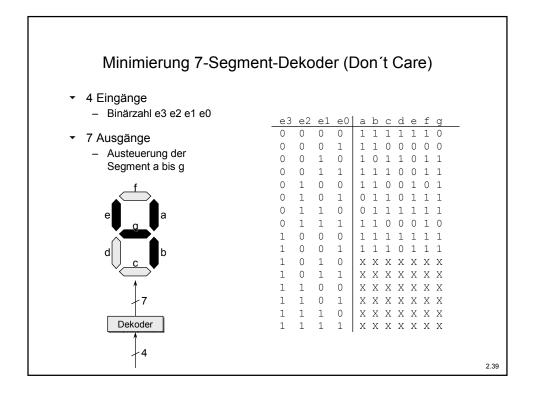

# Wahrheitstabelle 7-Segment-Dekoder

- ▼ 4 Eingänge

- Binärzahl  $e_3 e_2 e_1 e_0$

- 7 Ausgänge

- Austeuerung der Segment a bis g

| e <sub>3</sub> | $e_2$ | e <sub>1</sub> | e <sub>0</sub> | a : | b | С | d | е | f | g |  |

|----------------|-------|----------------|----------------|-----|---|---|---|---|---|---|--|

| 0              | 0     | 0              | 0              |     |   |   |   |   |   |   |  |

| 0              | 0     | 0              | 1              |     |   |   |   |   |   |   |  |

| 0              | 0     | 1              | 0              |     |   |   |   |   |   |   |  |

| 0              | 0     | 1              | 1              |     |   |   |   |   |   |   |  |

| 0              | 1     | 0              | 0              |     |   |   |   |   |   |   |  |

| 0              | 1     | 0              | 1              |     |   |   |   |   |   |   |  |

| 0              | 1     | 1              | 0              |     |   |   |   |   |   |   |  |

| 0              | 1     | 1              | 1              |     |   |   |   |   |   |   |  |

| 1              | 0     | 0              | 0              |     |   |   |   |   |   |   |  |

| 1              | 0     | 0              | 1              |     |   |   |   |   |   |   |  |

| 1              | 0     | 1              | 0              |     |   |   |   |   |   |   |  |

| 1              | 0     | 1              | 1              |     |   |   |   |   |   |   |  |

| 1              | 1     | 0              | 0              |     |   |   |   |   |   |   |  |

| 1              | 1     | 0              | 1              |     |   |   |   |   |   |   |  |

| 1              | 1     | 1              | 0              |     |   |   |   |   |   |   |  |

| 1              | 1     | 1              | 1              |     |   |   |   |   |   |   |  |

|                |       |                |                |     |   |   |   |   |   |   |  |

|                |       |                |                |     |   |   |   |   |   |   |  |

2 18

# 7-Segment-Dekoder (cont.)

▼ Wie erhält man boolesche Ausdrücke für a bis g?

$$a(e_3, e_2, e_1, e_0) =$$

$b(e_3, e_2, e_1, e_0) =$

$\vdots$

$g(e_3, e_2, e_1, e_0) =$

## 7-Segment-Dekoder (cont.)

▼ Gatterschaltung:

2.22

# Disjunktive und konjunktive Normalformen

- ▼ Disjunktive Normalform

- Summe von Produkten (minterme)

- ▼ Minterm

- 1 Zeile in Wahrheitstabelle

- Eingänge mit 1: e

- Eingänge mit 0: e negiert

- Konjunktive Normalform

- Produkt von Summen (maxterme)

- Maxterm

- 0 Zeile in Wahrheitstabelle

- Eingänge mit 1: e negiert

- Eingänge mit 0: e

| e2 | e1 | e0 | а |

|----|----|----|---|

| 0  | 0  | 0  | 0 |

| 0  | 0  | 1  | 0 |

| 0  | 1  | 0  | 1 |

| 0  | 1  | 1  | 1 |

| 1  | 0  | 0  | 1 |

| 1  | 0  | 1  | 0 |

| 1  | 1  | 0  | 1 |

| 1  | 1  | 1  | 0 |

# Boolesche Algebra

- ▼ Dualität zwischen

- Gatterschaltungen

- Booleschen Ausdrücken

- ▼ Positive Logik

- 0 = False

- 1 = True

- ▼ Gesetze

## Gesetze

▼ Operationen mit 0 und 1

$$X + 0 = X, X + 1 = 1$$

$X \cdot 0 = 0, X \cdot 1 = X$

▼ Idempotenz

$$X + X = X$$

$$X \cdot X = X$$

Komplementärgesetz

$$X + \overline{X} = 1$$

$$X \cdot \overline{X} = 0$$

### Gesetze (cont.)

▼ Kommutativitätsgesetz

$$X + Y = Y + X$$

$$X \cdot Y = Y \cdot X$$

Assoziativitätsgesetz

$$(X + Y) + Z = X + (Y + Z)$$

$$(X \cdot Y) \cdot Z = X \cdot (Y \cdot Z)$$

▼ Distributivgesetz

$$X \cdot (Y+Z) = X \cdot Y + X \cdot Z$$

$$X + (Y \cdot Z) = (X+Y) \cdot (X+Z)$$

2 28

### Gesetze (cont.)

Vereinfachungsgesetze

$$X \cdot Y + X \cdot \overline{Y} = X, (X + Y) \cdot (X + \overline{Y}) = X$$

$$X + X \cdot Y = X, X \cdot (X + Y) = X$$

$$(X + \overline{Y}) \cdot Y = X \cdot Y, (X \cdot \overline{Y}) + Y = X + Y$$

▼ DeMorgan's Gesetz

$$\overline{X + Y + \ldots + Z} = \overline{X} \cdot \overline{Y} \cdot \ldots \cdot \overline{Z}$$

$$\overline{X \cdot Y \cdot \ldots \cdot Z} = \overline{X} + \overline{Y} + \ldots + \overline{Z}$$

### **Umformung und Minimierung**

- ▼ Gründe

- Begrenzungen bei der Schaltungstiefe

- Minimaler Materialeinsatz

- Bestimmter Gattervorrat

- Elektrische Eigenschaften

- Platzbeschränkungen

- ...

- Algebraische Umformungen

- Algorithmische Verfahren

- Karnaugh-Diagramme (1-4 Eingangsvariablen, 1 Ausgang)

- Quine-McCluskey-Verfahren (n Eingänge, 1 Ausgang)

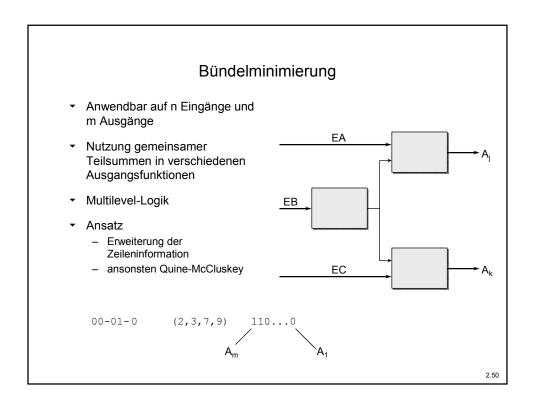

- Bündelminimierung (n Eingänge, m Ausgänge)

2.30

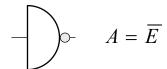

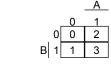

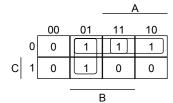

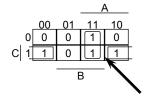

# Karnaugh-Diagramme

- ▼ Graphische Methode

- ▼ max. 4 Eingänge ABCD

- ▼ Übertragung der Wahrheitstabelle

- Position im Diagramm entspricht ABCD als Binärzahl

| Α | В | С                | a |               |

|---|---|------------------|---|---------------|

| 0 | 0 | 0                | 0 |               |

| 0 | 0 | 1<br>0<br>1<br>0 | 0 |               |

| 0 | 1 | 0                | 1 |               |

| 0 | 1 | 1                | 1 |               |

| 1 | 0 | 0                | 1 |               |

| 1 | 0 | 1                | 0 |               |

| 1 | 1 | 0                | 1 |               |

| 1 | 1 | 1                | 0 | = (2,3,4,6) = |

|     |    |    | <i>F</i> | ١  |

|-----|----|----|----------|----|

|     | 00 | 01 | 11       | 10 |

| 0   | 0  | 1  | 1        | 1  |

| C 1 | 0  | 1  | 0        | 0  |

|     |    | E  | 3        |    |

### Minimierung im Karnaugh-Diagramm

- ▼ Legende = Gray-Code

- benachbarte Zeilen und Spalten ändern sich nur in einem Bit

- Zusammenfassen von Gruppen zu 1, 2, 4 oder 8 Einsen

- 1 = keine Minimierung

- 2 = Term mit 2 aus 3Eingängen

- 4 = Term mit 1 aus 3Eingängen

- 8 = Funktion konstant 1

- ▼ Diagramm als Torus auffassen!

$$= \overline{A}B + B\overline{C} + A\overline{C}$$

2.32

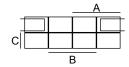

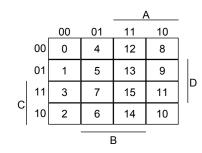

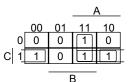

# 4 Eingänge

- Zusammenfassen von Gruppen zu 1, 2, 4, 8 oder 16 Einsen

- 1 = keine Minimierung

- 2 = Term mit 3 aus 4Eingängen

- 4 = Term mit 2 aus 4Eingängen

- 8 = Term mit 1 aus 4 Eingängen

- 16 = Funktion konstant 1

- ▼ Torus

#### Bemerkungen

- ▼ Bei bis zu vier Eingangsvariablen ideale Minimierungstechnik

- ▼ 5 und 6 Eingänge theoretisch auch möglich

- 5: zwei übereinander liegende 4er-Diagramme

- 6: vier übereinander liegende 4er-Diagramme

- insgesamt aber praktisch nicht handhabbar

- ▼ Konjunktive Minimalform ebenfalls möglich

- Zusammenfassen der 0-Gruppen

2.44

# Quine-McCluskey-Methode

- Algorithmisches Verfahren

- beliebig viele Eingänge

- 1 Ausgang

- ▼ 3 Schritte

- Initialisierung

- Ermittlung der Primimplikanten

- Ermittlung der minimalen Überdeckung

- Beispielfunktion

- Segment a

| eЗ | e2 | el | e0 | а | b | С | d | е | İ | g |  |

|----|----|----|----|---|---|---|---|---|---|---|--|

| 0  | 0  | 0  | 0  | 1 | 1 | 1 | 1 | 1 | 1 | 0 |  |

| 0  | 0  | 0  | 1  | 1 | 1 | 0 | 0 | 0 | 0 | 0 |  |

| 0  | 0  | 1  | 0  | 1 | 0 | 1 | 1 | 0 | 1 | 1 |  |

| 0  | 0  | 1  | 1  | 1 | 1 | 1 | 0 | 0 | 1 | 1 |  |

| 0  | 1  | 0  | 0  | 1 | 1 | 0 | 0 | 1 | 0 | 1 |  |

| 0  | 1  | 0  | 1  | 0 | 1 | 1 | 0 | 1 | 1 | 1 |  |

| 0  | 1  | 1  | 0  | 0 | 1 | 1 | 1 | 1 | 1 | 1 |  |

| 0  | 1  | 1  | 1  | 1 | 1 | 0 | 0 | 0 | 1 | 0 |  |

| 1  | 0  | 0  | 0  | 1 | 1 | 1 | 1 | 1 | 1 | 1 |  |

| 1  | 0  | 0  | 1  | 1 | 1 | 1 | 0 | 1 | 1 | 1 |  |

| 1  | 0  | 1  | 0  | 1 | 1 | 0 | 1 | 1 | 1 | 1 |  |

| 1  | 0  | 1  | 1  | 0 | 1 | 1 | 1 | 1 | 0 | 1 |  |

| 1  | 1  | 0  | 0  | 0 | 0 | 1 | 1 | 1 | 1 | 0 |  |

| 1  | 1  | 0  | 1  | 1 | 1 | 1 | 1 | 0 | 0 | 1 |  |

| 1  | 1  | 1  | 0  | 0 | 0 | 1 | 1 | 1 | 1 | 1 |  |

| 1  | 1  | 1  | 1  | 0 | 0 | 0 | 1 | 1 | 1 | 1 |  |

|    |    |    |    |   |   |   |   |   |   |   |  |

# 1. Initialisierung

Sortierung der Minterme aufsteigend nach Anzahl 1

> 0001 (1) 0010 (2) 0100 (4) 1000 (8) 0011 (3) 1001 (9) 1010 (10) 0111 (7) 1101 (13)

0000

(0)

2.46

# 2. Primimplikanten

- Vergleich jedes Element einer Gruppe mit allen Elementen der nächsten Gruppe

- Übernahme in die nächste Spalte, wenn nur in einer Position verschieden

- ▼ Gewählte Zeilen markieren (ok)

| 0000 | (0) ok  | 000-<br>00-0 | (0,1)<br>(0,2) |

|------|---------|--------------|----------------|

| 0001 | (1) ok  | 0-00         | (0, 4)         |

| 0010 | (2) ok  | -000         | (0,8)          |

| 0100 | (4) ok  |              |                |

| 1000 | (8) ok  | 00-1         | (1,3)          |

|      |         | -001         | (1, 9)         |

| 0011 | (3) ok  | 001-         | (2,3)          |

| 1001 | (9) ok  | -010         | (2,10)         |

| 1010 | (10) ok | 100-         | (8, 9)         |

|      |         | 10-0         | (8, 10)        |

| 0111 | (7) ok  |              |                |

| 1101 | (13) ok | 0-11         | (3,7)          |

|      |         | 1-01         | (9, 13)        |

|      |         |              |                |

#### Abbruchkriterium

- Markierung mit der nächsten Spalte wiederholen

- ▼ Bis auf eine Position gleich (- = -)

- ▼ Abbruch, wenn keine weitere Spalte entsteht

```

000-

(0,1) ok

00-- (0,1,2,3) *

0 - 0

(0,2) ok

-00- (0,1,8,9) *

0-00 (0,4) *

-0-0 (0,2,8,10) *

-000

(0,8) ok

00-1 (1,3) ok

-001 (1,9) ok

001- (2,3) ok

-010 (2,10) ok

100- (8,9) ok

10-0 (8,10) ok

0-11 \quad (3,7) \quad *

1-01 (9,13) *

```

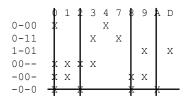

# 3. Minimale Überdeckung

Sammeln der mit \* markierten Primimplikanten:

```

0-00 (0,4)

0-11 (3,7)

1-01 (9,13)

00-- (0,1,2,3)

-00- (0,1,8,9)

-0-0 (0,2,8,10)

```

- Nur einmal markierte Spalten suchen

- essentielle Primimplikanten

- Zusätzliche Spalten streichen

- Schritt auf unmarkierten Spalten wiederholen

```

0 1 2 3 4 7 8 9 A D

0-00 X X X

0-11 X X X

1-01 X X X

00-- X X X X

-00- X X X X

X X

```

2.49

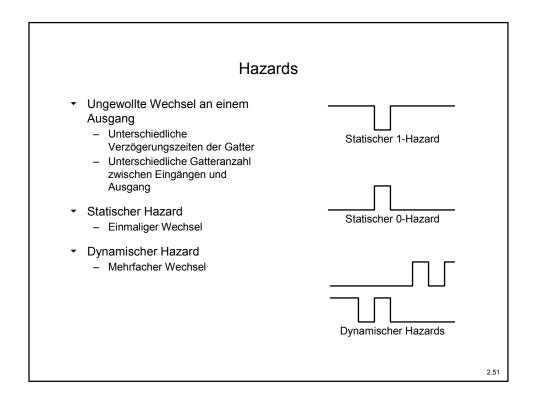

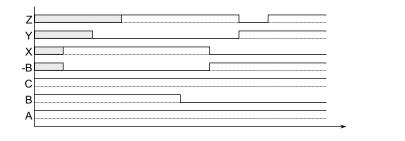

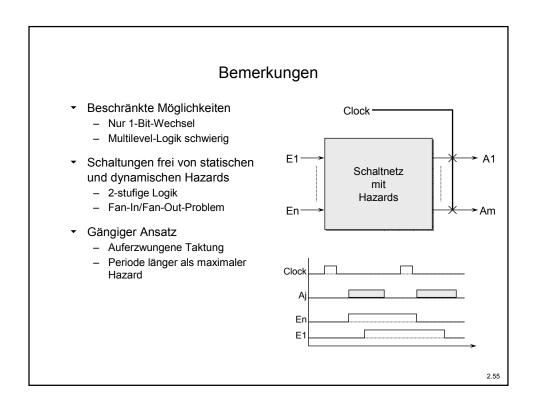

# Statischer Hazard

- ▼ Nur 1-Bit-Wechsel

- ▼ Beispiel

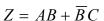

$$Z = AB + \overline{B}C$$

- Wechsel 111 nach 011 (ABC)

2.52

# Eliminierung statischer Hazards

- ▼ Grundlage Karnaugh-Diagramm

- ▼ Merkmal für 1-Hazard

- Wechsel des Primimplikanten bei 1-Bitwechsel der Eingabe

- Lösung: Redundante Implikanten

- ▼ Merkmal für 0-Hazard

- Karnaugh-Diagramm für konjunktive Normalform

- Analog 1-Hazard

- Eliminierung statischer Hazards auch in mehrstufigen Schaltungen möglich

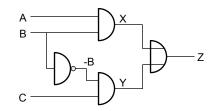

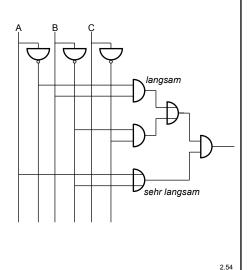

## Dynamischer Hazard

Beispiel

$$(\overline{A}B + \overline{B}\overline{C})(A + \overline{B})$$

- Wechsel 000 nach 010 (ABC)

- ▼ Grund

- Unterschiedlich lange Wege von einem Eingang zu einem Ausgang

- ▼ Eliminierung schwierig

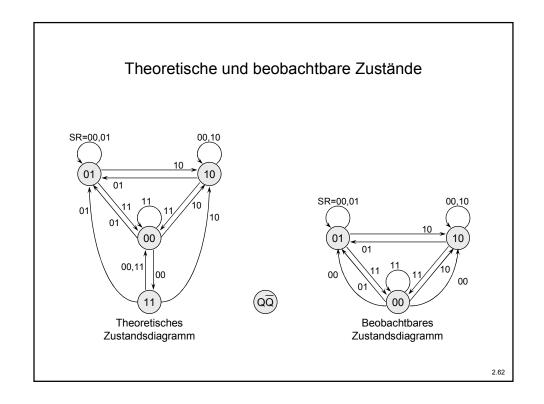

#### Schaltwerke

- Kombinatorische Schaltnetze

- Ausgang hängt nur von den Eingängen ab

- Unterschiedliche Laufzeiten (Hazard-Problematik)

- Schaltwerk

- Ausgang hängt von den Eingängen und den vorherigen Ausgaben ab

- Aspekte

- Speichern möglich

- Synchron / Asynchron

- Schwingungen

- Metastabilität

- Selbsttaktung

- ▼ Elementarbausteine

- Latch

- Flip-Flop

2.56

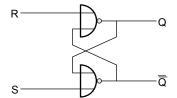

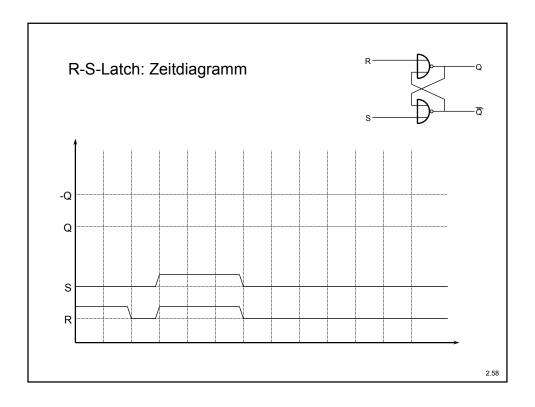

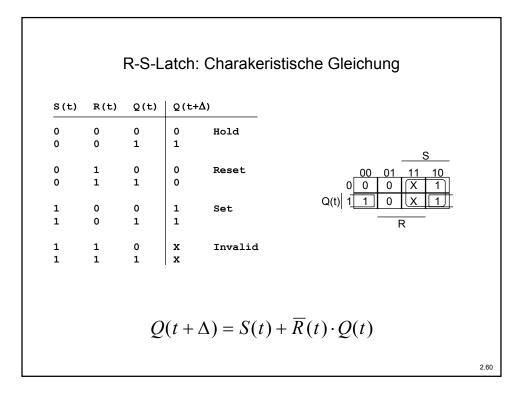

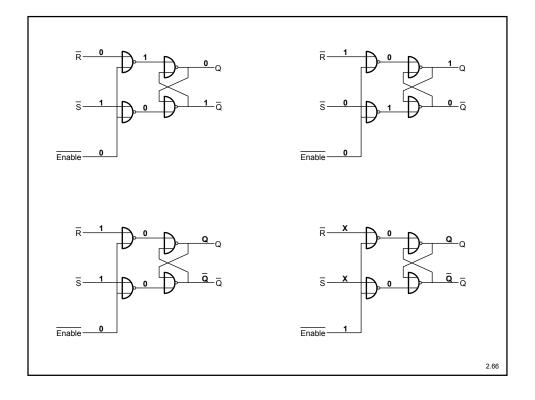

# Elementarspeicher: R-S-Latch

- Kreuzverschaltete NOR-Gatter

- R: Reset

- S: Set

- Ausgang Q mit Komplement

- Ausgang zurücksetzen

- R=1, S=0

- Ausgang setzen

- R=0, S=1

- ▼ Wert speichern

- R=0, S=0

#### Probleme

- ▼ Verbotene Eingangskombination

- R=S=1

- Beide Ausgänge sind 0

- ▼ Verbotener Übergang

- R und S gleichzeitig von 1 nach 0

- Oszillation der Ausgänge

- Wie lang kann die Oszillation dauern?

- Theoretisch?

- Praktisch?

- ▼ Race-Condition

| S | R | Q         |

|---|---|-----------|

| 0 | 0 | Speichern |

| 0 | 1 | 0         |

| 1 | 0 | 1         |

| 1 | 1 | Instabil  |

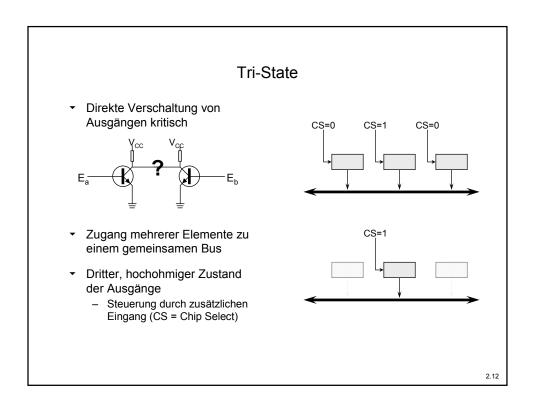

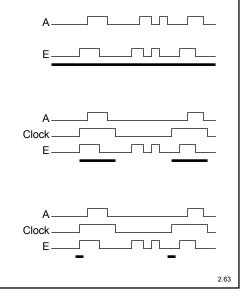

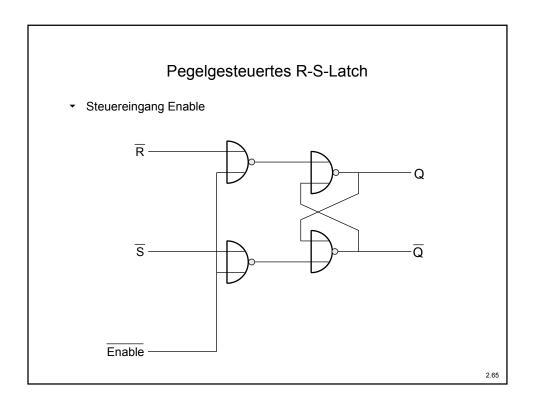

## Steuerungsarten

- Wann wirken die Eingänge auf die Ausgänge

- Drei Varianten

- Ungesteuert (R-S-Latch)

- Pegelgesteuert

- Flankengesteuert

- Positiv (0 nach 1)

- Negativ (1 nach 0)

- ▼ Zusätzliche Steuerungsleitung

- Enable

- Clock

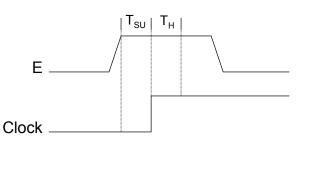

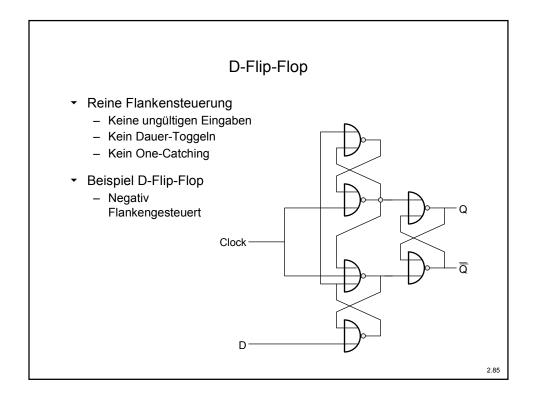

# Flankensteuerung

- Stabiler Eingang in einem Zeitfenster vor dem Flankenwechsel

- Setup-Zeit: T<sub>SU</sub>

- Hold-Zeit: T<sub>H</sub>

- Verhalten ansonst undefiniert

- Typische Werte (TTL)

- T<sub>SU</sub> = 20nsT<sub>H</sub> = 5ns

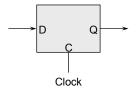

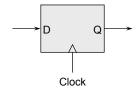

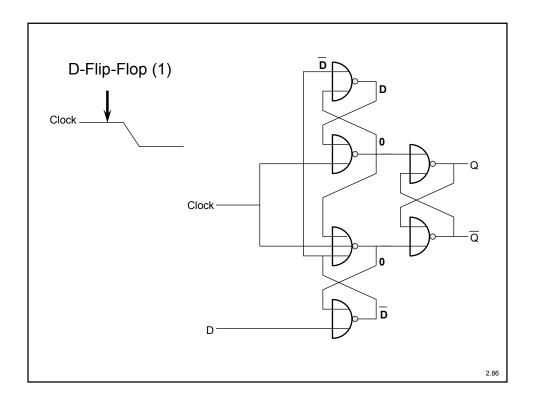

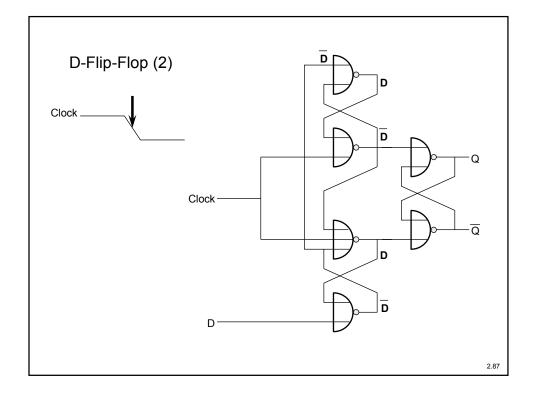

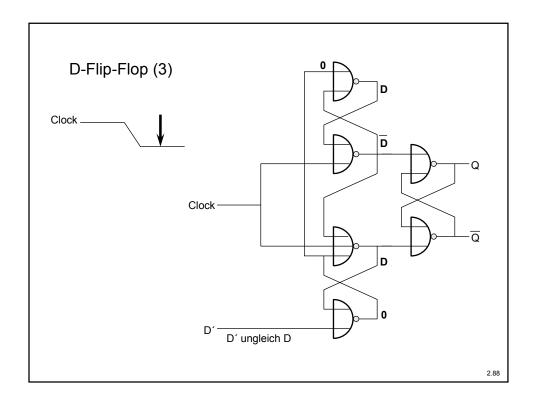

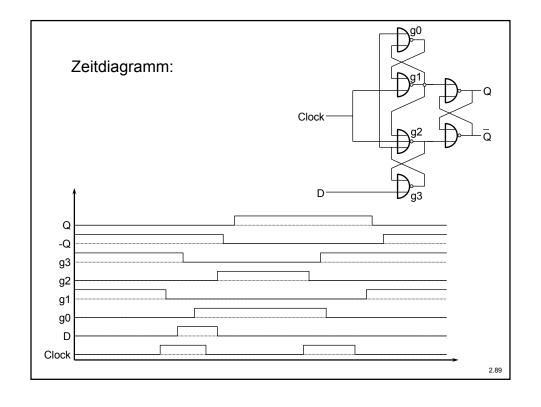

# Latch vs. Flip-Flop

- ▼ Latch

- Ungesteuert

- Pegelgesteuert

- Änderung der Ausgänge bei Änderung der Eingänge

- ▼ Flip-Flop

- Positiv flankengesteuert

- Negativ flankengesteuert

- Master/Slave

- Änderung der Ausgänge wird durch den Steuerungseingang getriggert

2.67

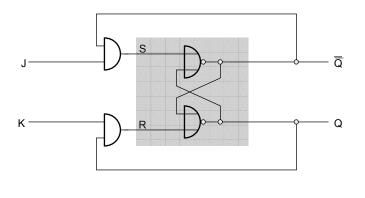

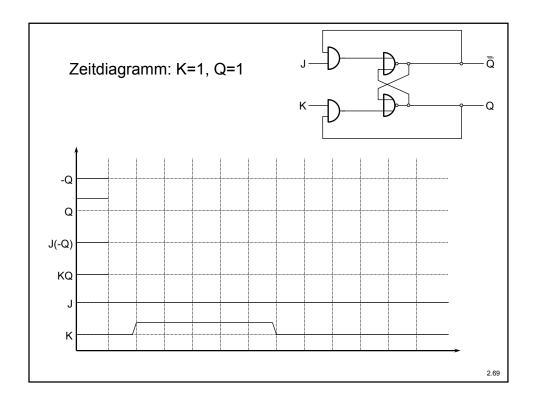

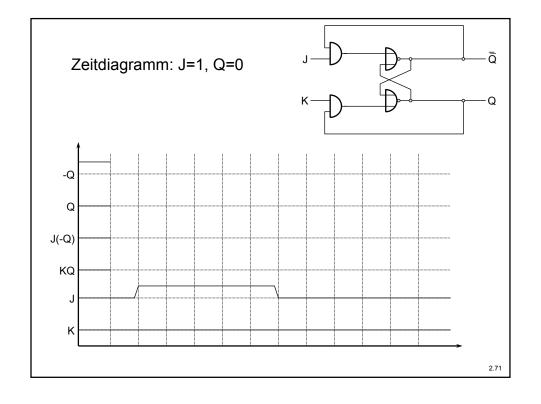

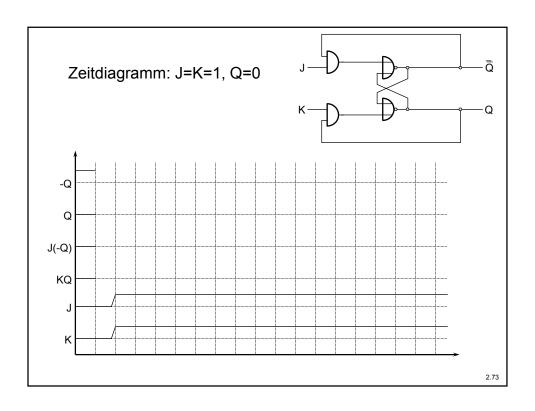

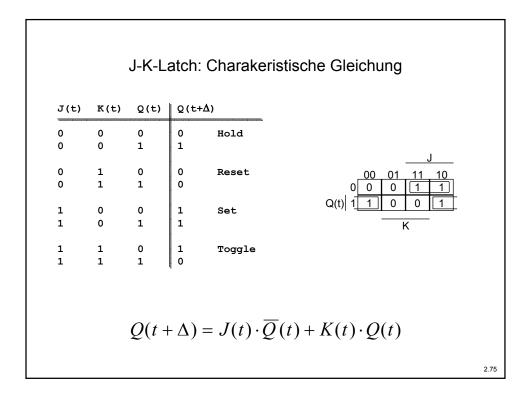

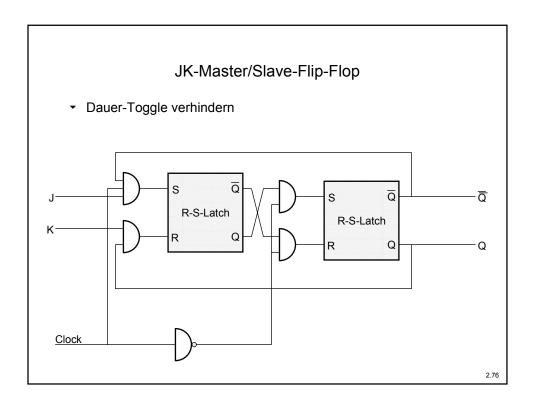

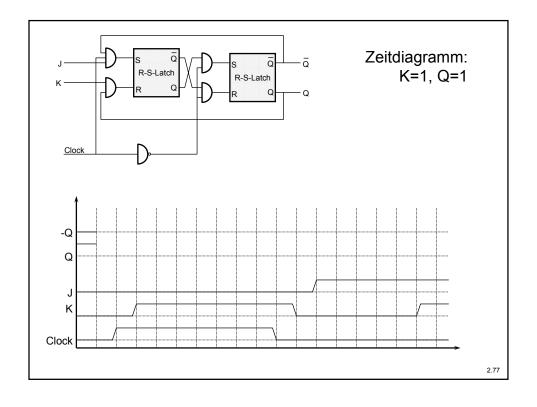

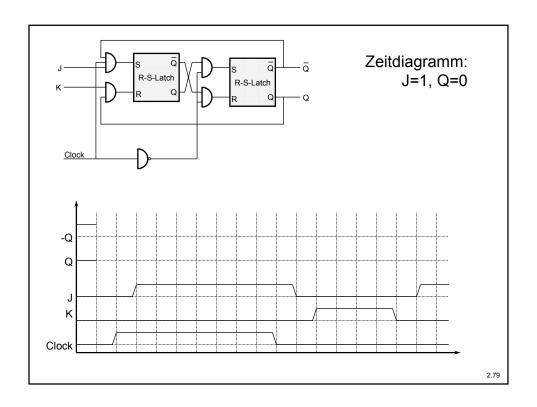

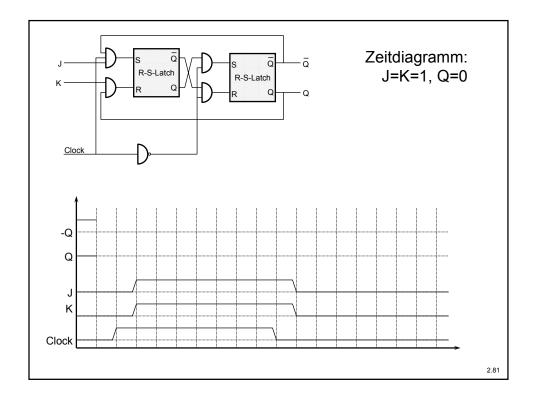

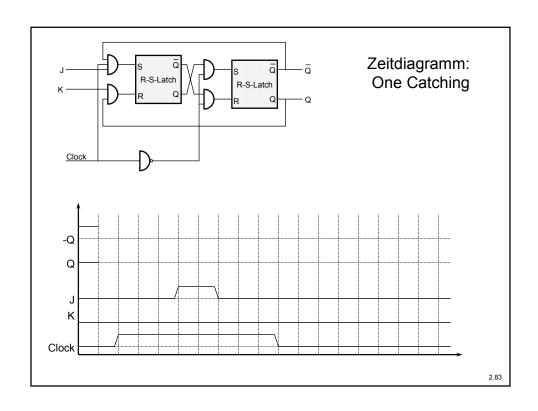

## JK-Latch

- ▼ Erweiterung eines R-S-Latch

- Ungültige Eingabe R=S=1 verhindern

- ▼ Was passiert bei J=K=1?

#### Programmierbare Logik

- ▼ Realisierung von Schaltnetzen und Schaltwerken

- Aufbau mit Hilfe von TTL- und CMOS-ICs aufwendig

- Große Anzahl an Bausteinen

- Hoher Platz- und Stromverbrauch

- Geringe Integrationsdichte

- ▼ IC mit 1000 AND mit jeweils 2 Eingängen = 3002 Pins

- "Programmierbare Bausteine"

- Genügend Eingängen

- Genügend Ausgängen

- Ausreichende Programmierbarkeit

- Zweistufige Normalformen

2.90

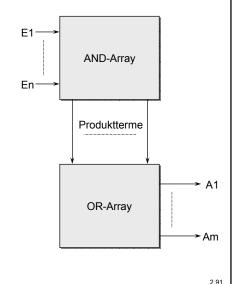

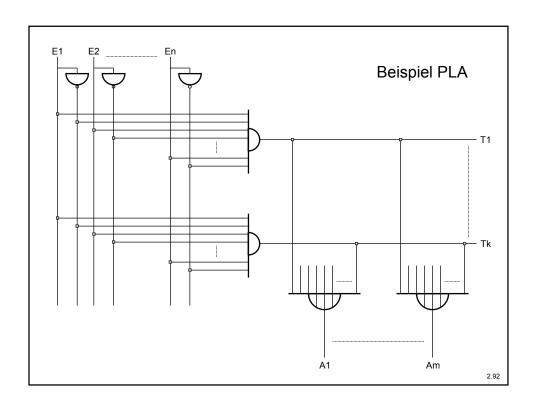

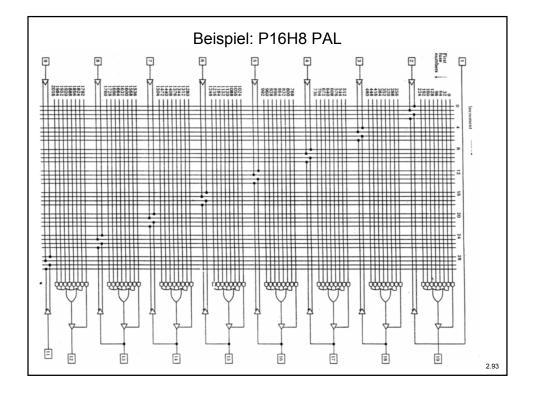

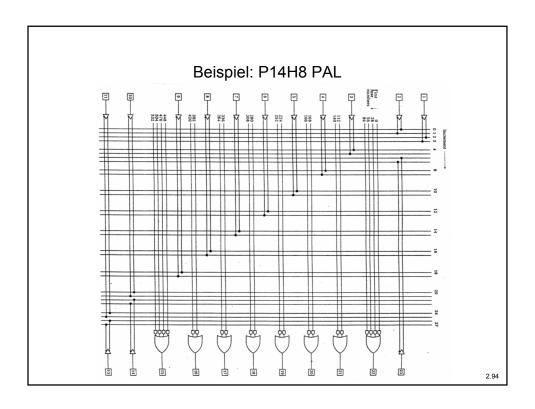

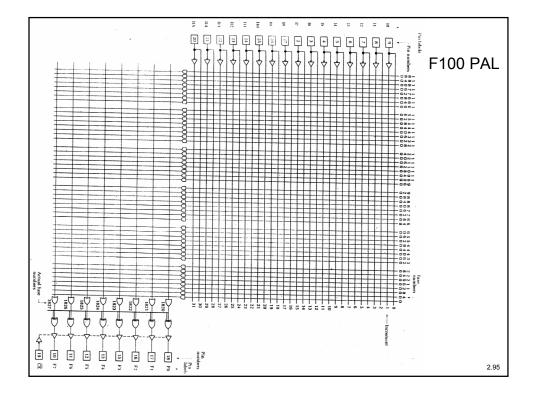

#### PLA und PAL

- Programmierbare disjunktive Normalform

- n Eingängen

- m Ausgängen

- k Terme

- ▼ n,m und k vom jeweiligen Baustein abhängig

- ▼ PLA = Programmable Logic Array

- UND- und ODER-Array programmierbar

- ▼ PAL = Programmable Array Logic

- Nur UND-Array programmierbar

- ▼ Programmieren

- Höhere Programmierspannung

- "Durchbrennen" einer Verbindung